Former Research Area and projects during 2015-2021 in PSU

Micro-interconnect reliability and Macro joining and metal additive manufacturing

Microstructure Signature Evolution in Solder Joints, Solder Bumps, and Micro-Bumps Interconnection in Large 2.5D FCBGA Package during Thermo-Mechanical Cycling (Juniper networks)

How to read the language of interconnect microstructure

Thermal cycling performance enhancement using reworkable edgebond material

To enhance the mechanical stability and robust shock performance an adhesion bond metal was developed to apply at the corners of the large 65x65mm component and 12x12 WLCSP for performance improvements.

Wafer Level chip scale package thermal cycling performance degradation mechanism study

Wafer level components are high stress components and have limitation with thermo-mechanical fatigue on printed circuit boards due to CTE mismatch. Understanding the degradation mechanism based on localized recrystallization induced by Sn anisotropical behavior enable us to develop an anti degradation solution for higher reliability and long term lifecycle performance.

Effective and Application-Specific Evaluation of Low-k Dielectric Integration Integrity using Copper Pillar Shear Testing

Using Cu pillar control shearing to reveal instability in interconnect layers

Joint separation during z-axis thermal expansion mechanism study (Cisco) Impact of VIPPO PCB configuration

Solder Volume Effect and NCF effect on Electromigration Failure Mechanism of Cu/Sn-Ag Microbump

Identification of the failure mechanism

Solder ball gliding : Investigation of the driving force and mechanism (AMD) Compression stress induced Sn slip system study

Development of Micro-probe high speed bonding technology for automotive semiconductor wafer test (Korea Instrument and KETI)

MEMS microprobe structure stability and interface analysis

Development of local degradation index for thermal cycling joints based on pre-crack EBSD analysis (Intel and OMI)

Proactive lifetime assessment

Cu paste Interface High Thermal Conductivity Material Development with Sub 250oC Process Temperature for EV/HEV Power Module Application (MK Electron and KETI)

Cu and Cu-Ag paste sintering mechanism study

Silicon die dielectric instability and variation detection : Impact of temperature on bump shear stability (Juniper Networks)

Cu pillar shear and new test methodology development

Heatsink compression induced stress impact on solder joint reliability: Finding the optimized compression level for heatsink installation (industry supplier)

Max force guideline study

Solder joint separation mechanism study using high temperature single joint pull testing and interface microstructure analysis (industry supplier)

Surface finish effect study

Reliability test and analysis of Low temperature solder & Cu core plating ball (MK Electron and Zymet)

Sn-58Bi and micro element effect

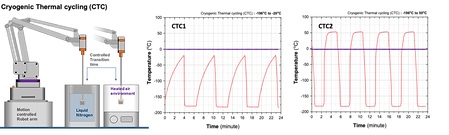

Micro interconnect mechanical stability study in Cryogenic temperature environment using single joint shear : Cryogenic Thermal cycling (CTC) (Nordson Dage)

Sub-zero and liquid nitrogen temperature interconnect stability study. Aplha to beta tin phase transformation study

Impact of current stressing on Sn based Single joint shear stability (MK Electron and Zymet)

New testing methodology for high current induced interconnect testing.

Mechanical shock induced failure analysis in electronic devices with low melting temperature solder (MK electron)

Isothermal aging and shock performance study

Sn grain orientation study on Sn base solder joints using Orientation Imaging microscopy and Synchrotron measurement,

To find the direct correlation between Sn grain orientation and thermal cycling phenomenon. By identifying the direct correlation between High stress and low stress package difference in grain structure development the sub-grain boundary role was able to explained. Also the Solder joint in-situ melting and solidification synchrotron measurement was able to perform, showing the internal stress build up during in-situ thermal cycling.

Investigation of the impact of Cu via Si interfaces on the stability of stacked die structures

Silicon TSV structure in high bandwidth memory devices is a new concept recently implemented into memory devices which need higher speed and functionality expecially in 2.5D and 3D interposer electronic components and devices. The Cu via structure interface between the via and the Si can be impacted by the constant current flow resulting in a interface migration/sliding. This project is a collaboration project with Prof. Dutta in Washington State University funded by Cisco.

Electromigration induced Joule heating effect on Solder interconnections reliability

Microbump and solder bump stability under long-term high current environment.

-------------------------------

Aluminum alloy mechanical property tuning using Cold Metal Transfer (CMT) advanced welding arc mode

mechanical and interface stability study

1018 steel + 308 Stainless steel dissimilar material additive manufacturing for enhanced cryogenic mechanical performance

Interface modification via heating and cooling rate control for higher toughness at cryogenic temperature

Inconel 718 additive manufacturing using Cold Metal Transfer (CMT)

Interface property tuning in 308L stainless steel using integrated additive manufacturing process : CMT, Ultrasonic Impact treatment and Electro-spark deposition